Clock control register.

#include <rcc.hpp>

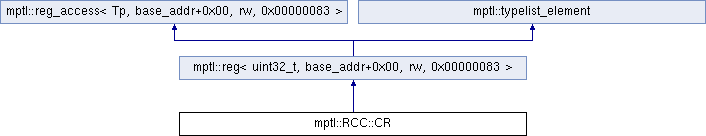

Inheritance diagram for mptl::RCC::CR:

Public Types | |

| using | PLLI2SRDY = regbits< type, 27, 1 > |

| PLLI2S clock ready flag. More... | |

| using | PLLI2SON = regbits< type, 26, 1 > |

| PLLI2S enable. More... | |

| using | PLLRDY = regbits< type, 25, 1 > |

| Main PLL clock ready flag. More... | |

| using | PLLON = regbits< type, 24, 1 > |

| Main PLL enable. More... | |

| using | CSSON = regbits< type, 19, 1 > |

| Clock security system enable. More... | |

| using | HSEBYP = regbits< type, 18, 1 > |

| HSE clock bypass. More... | |

| using | HSERDY = regbits< type, 17, 1 > |

| HSE clock ready flag. More... | |

| using | HSEON = regbits< type, 16, 1 > |

| HSE clock enable. More... | |

| using | HSICAL = regbits< type, 8, 8 > |

| Internal high-speed clock calibration. More... | |

| using | HSITRIM = regbits< type, 3, 5 > |

| Internal high-speed clock trimming. More... | |

| using | HSIRDY = regbits< type, 1, 1 > |

| Internal high-speed clock ready flag. More... | |

| using | HSION = regbits< type, 0, 1 > |

| Internal high-speed clock enable. More... | |

Public Types inherited from mptl::reg< uint32_t, base_addr+0x00, rw, 0x00000083 > Public Types inherited from mptl::reg< uint32_t, base_addr+0x00, rw, 0x00000083 > | |

| typedef reg< Tp, base_addr+0x00, rw, 0x00000083 > | type |

| typedef type | reg_type |

| typedef regbits< type, 0, sizeof(Tp) *8 > | regbits_type |

| typedef Tp | value_type |

| typedef regmask< reg_type, 0, 0 > | neutral_regmask |

Public Types inherited from mptl::reg_access< Tp, base_addr+0x00, rw, 0x00000083 > Public Types inherited from mptl::reg_access< Tp, base_addr+0x00, rw, 0x00000083 > | |

| typedef Tp | value_type |

Member Typedef Documentation

◆ CSSON

| using mptl::RCC::CR::CSSON = regbits< type, 19, 1 > |

◆ HSEBYP

| using mptl::RCC::CR::HSEBYP = regbits< type, 18, 1 > |

◆ HSEON

| using mptl::RCC::CR::HSEON = regbits< type, 16, 1 > |

◆ HSERDY

| using mptl::RCC::CR::HSERDY = regbits< type, 17, 1 > |

◆ HSICAL

| using mptl::RCC::CR::HSICAL = regbits< type, 8, 8 > |

◆ HSION

| using mptl::RCC::CR::HSION = regbits< type, 0, 1 > |

◆ HSIRDY

| using mptl::RCC::CR::HSIRDY = regbits< type, 1, 1 > |

◆ HSITRIM

| using mptl::RCC::CR::HSITRIM = regbits< type, 3, 5 > |

◆ PLLI2SON

| using mptl::RCC::CR::PLLI2SON = regbits< type, 26, 1 > |

◆ PLLI2SRDY

| using mptl::RCC::CR::PLLI2SRDY = regbits< type, 27, 1 > |

◆ PLLON

| using mptl::RCC::CR::PLLON = regbits< type, 24, 1 > |

◆ PLLRDY

| using mptl::RCC::CR::PLLRDY = regbits< type, 25, 1 > |

The documentation for this struct was generated from the following file:

- arch/arm/cortex/stm32/f4/include/arch/reg/rcc.hpp

1.8.13

1.8.13