AHB1 peripheral clock register.

#include <rcc.hpp>

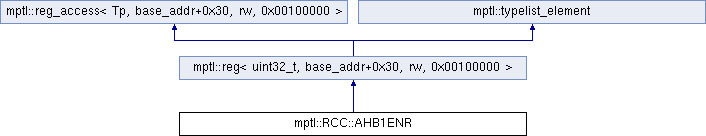

Inheritance diagram for mptl::RCC::AHB1ENR:

Public Types | |

| using | OTGHSULPIEN = regbits< type, 30, 1 > |

| USB OTG HSULPI clock enable. More... | |

| using | OTGHSEN = regbits< type, 29, 1 > |

| USB OTG HS clock enable. More... | |

| using | ETHMACPTPEN = regbits< type, 28, 1 > |

| Ethernet PTP clock enable. More... | |

| using | ETHMACRXEN = regbits< type, 27, 1 > |

| Ethernet Reception clock enable. More... | |

| using | ETHMACTXEN = regbits< type, 26, 1 > |

| Ethernet Transmission clock enable. More... | |

| using | ETHMACEN = regbits< type, 25, 1 > |

| Ethernet MAC clock enable. More... | |

| using | DMA2EN = regbits< type, 22, 1 > |

| DMA2 clock enable. More... | |

| using | DMA1EN = regbits< type, 21, 1 > |

| DMA1 clock enable. More... | |

| using | BKPSRAMEN = regbits< type, 18, 1 > |

| Backup SRAM interface clock enable. More... | |

| using | CRCEN = regbits< type, 12, 1 > |

| CRC clock enable. More... | |

| using | GPIOIEN = regbits< type, 8, 1 > |

| IO port I clock enable. More... | |

| using | GPIOHEN = regbits< type, 7, 1 > |

| IO port H clock enable. More... | |

| using | GPIOGEN = regbits< type, 6, 1 > |

| IO port G clock enable. More... | |

| using | GPIOFEN = regbits< type, 5, 1 > |

| IO port F clock enable. More... | |

| using | GPIOEEN = regbits< type, 4, 1 > |

| IO port E clock enable. More... | |

| using | GPIODEN = regbits< type, 3, 1 > |

| IO port D clock enable. More... | |

| using | GPIOCEN = regbits< type, 2, 1 > |

| IO port C clock enable. More... | |

| using | GPIOBEN = regbits< type, 1, 1 > |

| IO port B clock enable. More... | |

| using | GPIOAEN = regbits< type, 0, 1 > |

| IO port A clock enable. More... | |

Public Types inherited from mptl::reg< uint32_t, base_addr+0x30, rw, 0x00100000 > Public Types inherited from mptl::reg< uint32_t, base_addr+0x30, rw, 0x00100000 > | |

| typedef reg< Tp, base_addr+0x30, rw, 0x00100000 > | type |

| typedef type | reg_type |

| typedef regbits< type, 0, sizeof(Tp) *8 > | regbits_type |

| typedef Tp | value_type |

| typedef regmask< reg_type, 0, 0 > | neutral_regmask |

Public Types inherited from mptl::reg_access< Tp, base_addr+0x30, rw, 0x00100000 > Public Types inherited from mptl::reg_access< Tp, base_addr+0x30, rw, 0x00100000 > | |

| typedef Tp | value_type |

Member Typedef Documentation

◆ BKPSRAMEN

| using mptl::RCC::AHB1ENR::BKPSRAMEN = regbits< type, 18, 1 > |

◆ CRCEN

| using mptl::RCC::AHB1ENR::CRCEN = regbits< type, 12, 1 > |

◆ DMA1EN

| using mptl::RCC::AHB1ENR::DMA1EN = regbits< type, 21, 1 > |

◆ DMA2EN

| using mptl::RCC::AHB1ENR::DMA2EN = regbits< type, 22, 1 > |

◆ ETHMACEN

| using mptl::RCC::AHB1ENR::ETHMACEN = regbits< type, 25, 1 > |

◆ ETHMACPTPEN

| using mptl::RCC::AHB1ENR::ETHMACPTPEN = regbits< type, 28, 1 > |

◆ ETHMACRXEN

| using mptl::RCC::AHB1ENR::ETHMACRXEN = regbits< type, 27, 1 > |

◆ ETHMACTXEN

| using mptl::RCC::AHB1ENR::ETHMACTXEN = regbits< type, 26, 1 > |

◆ GPIOAEN

| using mptl::RCC::AHB1ENR::GPIOAEN = regbits< type, 0, 1 > |

◆ GPIOBEN

| using mptl::RCC::AHB1ENR::GPIOBEN = regbits< type, 1, 1 > |

◆ GPIOCEN

| using mptl::RCC::AHB1ENR::GPIOCEN = regbits< type, 2, 1 > |

◆ GPIODEN

| using mptl::RCC::AHB1ENR::GPIODEN = regbits< type, 3, 1 > |

◆ GPIOEEN

| using mptl::RCC::AHB1ENR::GPIOEEN = regbits< type, 4, 1 > |

◆ GPIOFEN

| using mptl::RCC::AHB1ENR::GPIOFEN = regbits< type, 5, 1 > |

◆ GPIOGEN

| using mptl::RCC::AHB1ENR::GPIOGEN = regbits< type, 6, 1 > |

◆ GPIOHEN

| using mptl::RCC::AHB1ENR::GPIOHEN = regbits< type, 7, 1 > |

◆ GPIOIEN

| using mptl::RCC::AHB1ENR::GPIOIEN = regbits< type, 8, 1 > |

◆ OTGHSEN

| using mptl::RCC::AHB1ENR::OTGHSEN = regbits< type, 29, 1 > |

◆ OTGHSULPIEN

| using mptl::RCC::AHB1ENR::OTGHSULPIEN = regbits< type, 30, 1 > |

The documentation for this struct was generated from the following file:

- arch/arm/cortex/stm32/f4/include/arch/reg/rcc.hpp

1.8.13

1.8.13