Flash access control register.

#include <flash.hpp>

|

| using | DCRST = regbits< type, 12, 1 > |

| | Data cache reset. More...

|

| |

| using | ICRST = regbits< type, 11, 1 > |

| | Instruction cache reset. More...

|

| |

| using | DCEN = regbits< type, 10, 1 > |

| | Data cache enable. More...

|

| |

| using | ICEN = regbits< type, 9, 1 > |

| | Instruction cache enable. More...

|

| |

| using | PRFTEN = regbits< type, 8, 1 > |

| | Prefetch enable. More...

|

| |

| using | LATENCY = regbits< type, 0, 3 > |

| | Latency. More...

|

| |

| typedef reg< Tp, base_addr+0x00, rw, 0x00000000 > | type |

| |

| typedef type | reg_type |

| |

| typedef regbits< type, 0, sizeof(Tp) *8 > | regbits_type |

| |

| typedef Tp | value_type |

| |

| typedef regmask< reg_type, 0, 0 > | neutral_regmask |

| |

| typedef Tp | value_type |

| |

◆ DCEN

◆ DCRST

◆ ICEN

◆ ICRST

◆ LATENCY

◆ PRFTEN

The documentation for this struct was generated from the following file:

- arch/arm/cortex/stm32/f4/include/arch/reg/flash.hpp

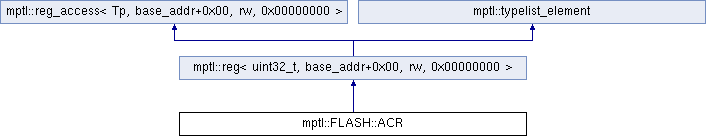

Public Types inherited from mptl::reg< uint32_t, base_addr+0x00, rw, 0x00000000 >

Public Types inherited from mptl::reg< uint32_t, base_addr+0x00, rw, 0x00000000 > Public Types inherited from mptl::reg_access< Tp, base_addr+0x00, rw, 0x00000000 >

Public Types inherited from mptl::reg_access< Tp, base_addr+0x00, rw, 0x00000000 > 1.8.13

1.8.13